# FABRICATION & PACKAGING SERVICES.

Our Technology Your Business

# **Wafer Fabrication Services**

Institute of Microelectronics (IME) Fab offers a broad range of services to our customers to meet the research and development (R&D) needs for semiconductor and related industries.

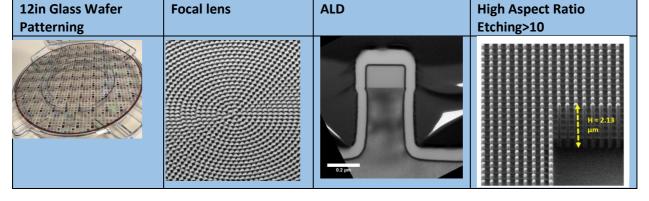

IME's Fab is located in-house and provides R&D services on micro-electro-mechanical systems (MEMS), microelectronics nanotechnology and bioelectronics applications. IME offers advanced lithography patterning services for 45nm half pitch features in small volume production in Class-10 clean room. Our Immersion Scanner is supported with metrology and defect tools and successfully demonstrated flat optics device functionality on 12" silicon and glass wafers.

# Lithography

i-line Steppers (<2um CD)</li>-ArF Immersion scanner (<45nm CD)</li>

# **Physical Vapor Deposition**

- Cu Seed

- Al/ AlO<sub>2</sub>

- Ti / TiN

- HfO<sub>2</sub> / HfN

### **Chemical Vapor Deposition**

- TEOS

- Silicon-Nitride

### **Electroplating (ECP)**

- Cu RDL, UBM

- TSV Cu Pillar

# **Bonding**

- Temporary/permanent

- Fusion

- Polymer

- Hybrid

- Metal

# **Metrology**

- Macro & Micro Defect Review

- Defect Review SEM

- Sidewall Roughness

- Surface Morphology

- Film Stress/ Warpage

- Film Thickness measurements

### **Furnace**

- Anneal

- Polymide , Dielectric Cure

### Etch

- Descum

- Silicon

- Oxide

- Silicon-Nitride

# **Customized Solutions**

- Specialty CVD/ PVD depositions

- New materials evaluations

- Deep machines learning applications

# Material Defects & Reliability Analysis Services

Material defects and reliability analysis (MDRA) are essential for microelectronics research, development and manufacturing. Our MDRA lab has the capabilities and cutting edge facilities to conduct world class research and development in semiconductor technology. We provide materials and process characterization, failure analysis and reliability test to support our industry partners in wafer fabrication, packaging, assembly and test.

| MDRA Tool Capabilities           |                                                                                                                                                                                         |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Tools Tool capability            |                                                                                                                                                                                         |  |  |  |  |

| 12" Probe station                | <ul> <li>Automation IV, CV measurement on 12" wafers</li> </ul>                                                                                                                         |  |  |  |  |

| FEI Double beam FIB              | <ul> <li>Up to 65nA Ga<sup>+</sup> beam current under 30KV</li> <li>High resolution SEM/STEM images (&lt;0.1nm)</li> <li>TEM sample preparation avaliable inside the machine</li> </ul> |  |  |  |  |

| FE- SEM                          | <ul> <li>High resolution SEM image with EBSD and EDX analysis (&lt;0.1nm)</li> <li>Probe in SEM to measure IV curve</li> </ul>                                                          |  |  |  |  |

| Ar Ion Milling/Polisher          | Sample preparation for SEM, FIB and optical microscope analysis                                                                                                                         |  |  |  |  |

| CSAM Sonix                       | <ul> <li>Transducers from 15 KHz to 230MHz for C-Scan/T-Scan analysis</li> <li>12" warp wafer compensation</li> </ul>                                                                   |  |  |  |  |

| Thermal Shock Chamber            | <ul> <li>Test standard JESD22-A104</li> <li>Temperature range ( -70°C to 300°C)</li> </ul>                                                                                              |  |  |  |  |

| ESD tester                       | Machine mode/Human body mode                                                                                                                                                            |  |  |  |  |

| High temperature storage chamber | <ul> <li>Test standard JESD22-A103</li> <li>Temperature storage up to 300°C</li> </ul>                                                                                                  |  |  |  |  |

| Thermal Shock (liquid to liquid) | <ul> <li>Test standard JESD22-A106</li> <li>Temperature range ( -65°C to 200°C)</li> </ul>                                                                                              |  |  |  |  |

| Thermal Humidity Chamber         | <ul> <li>Test standard JESD22-A101</li> <li>Temperature stress: 85 °C, relative humility stress: 85 %</li> </ul>                                                                        |  |  |  |  |

| FEI TEM (CM200)                  | <ul> <li>200KV transmission electron beam analysis (resolution &lt;0.14nm)</li> <li>EDX/EELS analysis</li> </ul>                                                                        |  |  |  |  |

| 3D X-Ray                         | <ul><li>None destructive 3D X-Ray imaging</li><li>High spatial resolution to 500nm</li></ul>                                                                                            |  |  |  |  |

| XB550                            | <ul> <li>FIB-SEM for 3D Analysis (resolution &lt;0.1nm)</li> </ul>                                                                                                                      |  |  |  |  |

# **FAB Capabilities**

| 12inch FAB Capabilities  |                                                                                                                                                                                                              |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Module                   | Unit Process capabilities                                                                                                                                                                                    |  |  |  |

| Photo<br>Lithography     | TSV Steppers with <2um patterning capability                                                                                                                                                                 |  |  |  |

|                          | Resist/Dielectric Polymer Coating                                                                                                                                                                            |  |  |  |

|                          | <ul> <li>Fine Lithography with Immersion Scanner for &lt;45nm patterning capability</li> </ul>                                                                                                               |  |  |  |

| Thin Films               | <ul> <li>PVD Seed Layer Deposition (Ti/Ta/Cu) (2x12/3x50/5x50/10x100/20x100um with max aspect ratio of 10~15)</li> </ul>                                                                                     |  |  |  |

|                          | <ul> <li>TSV Cu filling (2x12/3x50/5x50/10x100/20x100um with max aspect ratio of 15)</li> <li>Damascene Cu (CD&gt;=1um, max aspect ratio of 2)</li> </ul>                                                    |  |  |  |

|                          | <ul> <li>Cu RDL (Line/Space: 1/1um), Cu Pillar (CD &gt;10um, max aspect ratio of 2)</li> </ul>                                                                                                               |  |  |  |

|                          | <ul> <li>UBM Cu/Ni/SnAg (CD &gt;10um, max aspect ratio of 2)</li> </ul>                                                                                                                                      |  |  |  |

| Spin Coat                | <ul> <li>Coating of Under fill/Flux/Polymers with &amp; w/o Dicing Ring</li> </ul>                                                                                                                           |  |  |  |

|                          | Si etch for 5X50um & 10X100um TSV                                                                                                                                                                            |  |  |  |

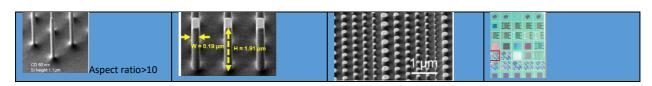

| Dry etch                 | <ul> <li>Si nano-structures etch of aspect ratio &gt;10 with &lt;60nm CD</li> <li>Metals etch with In-Situ PR Removal</li> </ul>                                                                             |  |  |  |

|                          | Ti/Cu etching                                                                                                                                                                                                |  |  |  |

| Clean                    | <ul> <li>Low temperature Photo Resist Stripping capability with Al/Cu compatible</li> <li>Post-RIE polymer removal</li> <li>Wafer front-side/backside cleaning</li> <li>Descum/Ex-Situ PR Removal</li> </ul> |  |  |  |

| CMP                      | Cu & Barrier Layer CMP                                                                                                                                                                                       |  |  |  |

|                          | Anodic, Solder, Polymer, Temporary & Permanent bonding                                                                                                                                                       |  |  |  |

| Bonding                  | Post Debond Cleaning                                                                                                                                                                                         |  |  |  |

|                          | <ul> <li>Dielectric &amp; PR Film thickness measurement with Spectroscopic Ellipsometry (SE) or<br/>Broadband Dual-Beam Spectrophotometry</li> </ul>                                                         |  |  |  |

|                          | Metal Sheet resistance measurement                                                                                                                                                                           |  |  |  |

|                          | Optical CD Measurement (<0.1nm accuracy)                                                                                                                                                                     |  |  |  |

|                          | CDSEM measurement (<0.35nm accuracy)                                                                                                                                                                         |  |  |  |

| 4011                     | Overlay measurement (<0.1nm accuracy)                                                                                                                                                                        |  |  |  |

|                          | Wafer bevel and backside defect inspection (<0.5um)                                                                                                                                                          |  |  |  |

| 12" In-Line<br>Metrology | Wafer macro and micro defect inspection and review                                                                                                                                                           |  |  |  |

| Metrology                | Unpattern wafer defect inspection (<26nm)                                                                                                                                                                    |  |  |  |

|                          | Pattern defect inspection (<30nm)  Pattern defect inspection (<30nm)                                                                                                                                         |  |  |  |

|                          | Defect SEM review with EDX and ADC (auto defect classification)      Cympofiles step beight measurement for step beight (FOOym)                                                                              |  |  |  |

|                          | Cu profiler step height measurement for step height <500um     Film stress or warnage 5 layer film parameter measurement                                                                                     |  |  |  |

|                          | Film stress or warpage 5 layer film parameter measurement     Side Wall roughness 3D ASM measurement with < 2A DMS noise layer.                                                                              |  |  |  |

|                          | Side Wall roughness 3D AFM measurement with <2A RMS noise level                                                                                                                                              |  |  |  |

|                          | <ul> <li>Surface morphology 2D AFM measurement with lateral accuracy</li> </ul>                                                                                                                              |  |  |  |

# **FAB Capabilities**

| 8inch FAB Capabilities |                                                                                                                                             |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Module                 | Unit Process capabilities                                                                                                                   |  |  |  |

| Photo<br>Lithography   | <ul> <li>I-line Resist Coating &amp; Patterning with 0.5um resolution and Front to Back<br/>Alignment</li> </ul>                            |  |  |  |

| Diffusion              | <ul> <li>Cu Annealing up to 600°C in N2 / 450°C in foaming gas</li> </ul>                                                                   |  |  |  |

|                        | Passivation Curing up to 600°C in N2                                                                                                        |  |  |  |

| Thin Films             | Specialty Metals - Mo/ AIN/ AI2O3/ HfO2 /ScAIN                                                                                              |  |  |  |

|                        | • Dielectric films - USG, SiN up to 400°C                                                                                                   |  |  |  |

|                        | • Cu RDL (Line/Space: 1/1um), Cu Pillar (CD >10um, max aspect ratio 2)                                                                      |  |  |  |

|                        | <ul> <li>TSV Cu filling (10x40 and 20x100 with max aspect ratio up to 15)</li> <li>Damascene Cu (CD&gt;=1um, max aspect ratio 2)</li> </ul> |  |  |  |

| Spin Coat              | • Polyimides, Organic Polymers                                                                                                              |  |  |  |

|                        | Anti-Stiction Coating                                                                                                                       |  |  |  |

| СМР                    | Cu CMP and Barrier Layer CMP                                                                                                                |  |  |  |

| Release<br>Process     | Oxide structures release capability for silicon depth up to 200um by XeF2                                                                   |  |  |  |

|                        | <ul> <li>Silicon structures release capability for sacrificial oxide depth up to 200um by HF<br/>Vapor</li> </ul>                           |  |  |  |

| Bonding                | Anodic, Solder, Polymer, Temporary & Permanent bonding (Low & High Force)                                                                   |  |  |  |

|                        | Post Debond Cleaning                                                                                                                        |  |  |  |

| In-line<br>Metrology   | <ul> <li>Infrared film thickness measurement with accuracy of +/-0.5mm</li> </ul>                                                           |  |  |  |

|                        | Sheet resistance measurement in the range of 50hms to 5MOhms.                                                                               |  |  |  |

| Electroplating Cu RDL (>2um line/space, 8/12inch) | Electroplating bump<br>(Cu/Ni/SnAg,<br>>20um, 8/12inch) | Cu Damascene<br>(>2um line/space,<br>8/12 inch) | Electroplating TSV (3-20um Via, 8/12 inch) |

|---------------------------------------------------|---------------------------------------------------------|-------------------------------------------------|--------------------------------------------|

|                                                   | 0 0                                                     |                                                 | 3x50 5x50 8x60 10x60 10x100 12x100 20x100  |

# **Packaging Design & Fabrication Services**

IME offers a wide range of advanced packaging technology solutions to address the above industry needs. Our platforms include 2.5D through-silicon interposer, 3D TSV, fan-out wafer level packaging, MEMS wafer level chip-scale packaging, fine-pitch Cu pillar, chip-on-wafer (direct Cu-to-Cu) bonding, electronic-photonic integration, as well as thermal solutions.

### **Services**

- Advanced packaging turnkey solutions for industry applications

- Thermo-mechanical, electrical, and thermal modeling and simulations to provide design guidelines

- TSV and through-silicon interposer (TSI) fabrication for 2.5D/3D IC packaging

- TSV fabrication and assembly for image sensor applications

- MEMS wafer level chip-scale packaging

- o FOWLP demonstration for new products

- FOWLP re-constructed wafers for equipment and material evaluations

### **Facilities**

- 3000m<sup>2</sup> of cleanrooms

- 200mm and 300mm TSV engineering line 0

- o 300mm FOWLP development line

- Assembly and packaging lab

- Package/board level reliability testing and failure analysis facilities

# IME's Multi-Chip 12" FOWLP Development Line

IME has state-of-the-art 300mm advanced wafer level packaging engineering line which can support various advanced wafer level packaging technologies development used in mobile, AI, Data Centre and IoT applications.

At IME, we offer end-to-end solutions in FOWLP & 2.5D/3D packaging and shorten the development cycle time for new applications. We also offer services in the area of wafer level fine pitch RDL of 2um/2um LW/LS, C4 solder bumping & Cu pillar micro bumping up to 20um pitch, temporary bonding & de-bonding, TSV fabrication etc.

IME's full fledge of development line comprises state-of-the-art tools including

- o PVD chamber for seed layer deposition

- PR track for coating and developing

- Stepper for lithography

- o Plating (Cu, Ni, Au, SnAg),

- Wet bench for PR stripping

- Spray etcher for seed etching

- N<sub>2</sub> furnace for curing

- o O<sub>2</sub> plasma for descum/etch

- o Flip-chip bonder for chip-to-wafer bonding

- o Molding tool for wafer level compression

- Warpage adjuster for molding tape de-bonding and warpage adjustment

- Backgrinder for wafer thinning

- Laser de-bonder for carrier de-bonding

- Solder jetter for solder ball attach

- Wafer dicer for wafer sawing

# **One-Stop Solution**

IME provides a one-stop solution from system concept, design integration, fabrication and testing to final packaging.

PDK (built on open access) supporting

# **Design Integration**

- Automatic guest die data import

- Die on interposer floor planning

- Automatic TSV placement

- Interposer auto routing (constraint driven, wire sizing)

# **Design Analysis**

- Package driven co-simulation with interconnects

- Signal integrity analysis

- -Design verification

- Design rule check

- Connectivity rule check

- Parasitic extraction (with TSV)

# **Research Support**

- Thermo-mechanical, electrical, and thermal modeling

- Material/failure analysis and reliability testing

# Your Ideal Partner for Realizing Advanced Packaging Solution

- o Accurate Package Process Design Kit for realizing TSI and FOWLP system designs

- Reference design implementation flow using multiple off-the-shelf sign-off quality EDA tools

- Physical implementation automation to reduce design and analysis turn-around time

IME is committed to protect customer's IP and confidentiality and provide the best supports to customers.

# **Contact Detail:**

2 Fusionopolis Way, #08-02 Innovis, Singapore 138634 (65) 6501 1800

An ISO 9001 and ISO 13485 Certified Organisation

www.a-star.edu.sg/ime