Spin Technology for Electronic Devices (SpEED)

Introduction

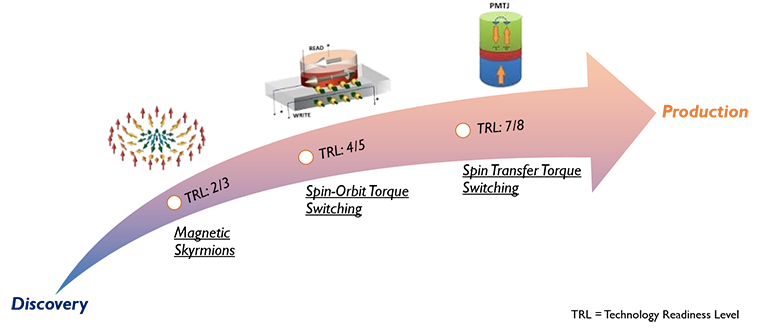

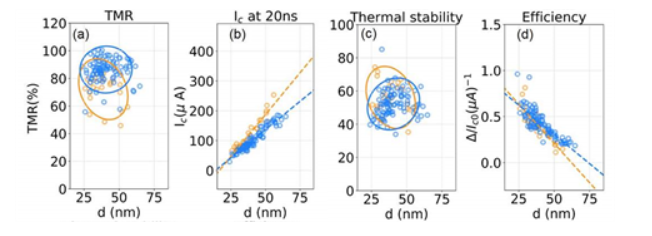

The SpEED (Spin Technology for Electronic Devices) programme aims to harness the potential of spin physics along three main directions: spin transfer torque, spin-orbit torque, and skyrmionic devices. Specifically, we aim to: (i) translate and integrate spin transfer torque (STT) technology into CMOS memory devices, (ii) demonstrate the use of ultra-fast, low-power field free spin orbit torque (SOT) in emerging memory devices and integrate them into CMOS chip, and (iii) to develop proof-of-concept skyrmionic devices towards multi-bit memory and synaptic computing.

Figures adapted from A. Soumyanarayanan et al., Nature 539, 509-517(2016).

The emergence of connected electronic devices with sensing and computing capabilities has ushered in the Internet of Things (IoT) era: the need for real-time decision making at the data source, or “edge intelligence”, has assumed increased significance. There is a growing need for developing high-performance computing hardware platforms with energy-efficient, GHz switching memory. Furthermore, the limitation of Moore’s law is being reached within conventional materials and present technologies. Thus, the quest to develop integrated, beyond-CMOS infocomm technology (ICT) platforms has also become increasingly important.

Next-gen ICT elements should 1) operate on an inherently shorter time scale enabling faster processing, 2) possess intrinsic stability and robustness for scalability, and 3) integrate seamlessly with conventional CMOS processes. While battery-powered edge devices would require non-volatile memory (NVM) platforms for scaling up such capabilities, emerging NVM solutions are read-optimised — inherently limited in high-performance switching characteristics required for these applications. Bridging this large performance gap first requires moving towards NVM technology platforms whose “normally-off” state can drastically reduce power consumption.

The field of spintronics is focused on exploiting electron spin as a degree of freedom for applications in solid-state devices. Earlier pioneering works successfully exploiting both giant magnetoresistance (GMR) and tunnelling magnetoresistance (TMR) effects and formed the basis of reading and memory storage applications in electronic devices today, through the use of GMR read heads in hard disk drives for storage and magnetic tunnelling junctions (MTJ).

Next generation spintronics technologies are sought to create devices with lower switching power, faster dynamics and higher endurance. One such avenue is via spin transfer torque (STT) — currently in manufacturing — where a spin polarised current can be used to control the magnetisation of a magnetic layer.

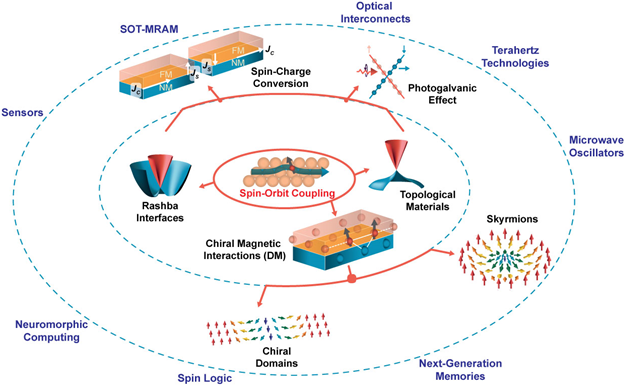

One particularly attractive avenue is the coupling of electron spin and momentum, known as spin-orbit coupling (SOC), recently found to be greatly enhanced at heavy metal (HM) – ferromagnet (FM) interfaces. Such interfaces are commonly used within existing MRAM stacks for incidental purposes. Interfacial SOC provides a fast, energy-efficient means to switch magnetisation, and creates new topological phases (topological materials, skyrmions etc.) that are robust at room temperature (RT). The practical utility of these recently discovered phenomena is imminent given the inherent CMOS compatibility of host materials.

Capabilities

.png?sfvrsn=76b646a0_2)

Achievements

Selected Publications and IPs

Spin Transfer Torque

- J. Lourembam et al.,“A non-collinear double MgO based perpendicular magnetic tunnel junction”, Appl. Phys. Lett. 113, 022403 (2018)

- J. Lourembam et al.,“Role of CoFeB thickness in electric field controlled sub-100 nm sized magnetic tunnel junctions”, AIP Advances, 8, 055915 (2018)

- M. Zeng et al.,“Large electric field modulation of magnetic anisotropy in MgO/CoFe/Ta structures with monolayer oxide insertion“, Appl. Phys. Lett. 113, 192404 (2018)

- J. Lourembam et al., “Thickness-Dependent Perpendicular Magnetic Anisotropy and Gilbert Damping in Hf/Co20Fe60B20/MgO Heterostructures” ,Phys. Rev. Appl. 10, 044057 (2018)

- A. Okada et al. ”Magnetization dynamics and its scattering mechanism in thin CoFeB films with interfacial anisotropy”, PNAS 114, 3815 (2017)

- Magnetoelectric device, method for forming a magnetoelectric device, and writing method for a magnetoelectric device. (US patent:US9601174B2)

- Magnetoresistive device and a writing method for a magnetoresistive device. (US patent: US9058885B2)

- Methods and circuit arrangements for determining resistances. (US patent: US9697894B2)

- Memory device with soft-decision decoding. (US patent: US8917540B2)

Spin Orbit Torque

- L. Huang et al.,“Engineering magnetic heterostructures to obtain large spin Hall efficiency for spin-orbit torque devices”, Appl. Phys. Lett. 113, 022402 (2018)

- M. Zeng et al.,“Interfacial electric field and spin-orbitronic properties of heavy-metal/CoFe bilayers”, Appl. Phys. Lett. 114, 012401 (2019)

- B. Chen et al.,“Field-free spin-orbit torque switching of a perpendicular ferromagnet with Dzyaloshinskii-Moriya interaction”, Appl. Phys. Lett. 114, 022401 (2019)

Skyrmions

- A.Soumyanarayanan et al., “Emergent phenomena induced by spin–orbit coupling at surfaces and interfaces”, Nature 539, 509–517 (2016).

- A.Soumyanarayanan et al., “Tunable room-temperature magnetic skyrmions in Ir/Fe/Co/Pt multilayers”, Nature Materials 16, 898-904 (2017).

- A.Yagil et al., “Stray field signatures of Néel textured skyrmions in Ir/Fe/Co/Pt multilayer films”, Appl. Phys. Lett. 112, 192403 (2018).

- P. Ho et al., Geometrically Tailored Skyrmions at Zero Magnetic Field in Multilayered Nanostructures”, Phys. Rev. Applied 11, 024064 (2019).

- M. Raju, A. Yagil et al., “The evolution of skyrmions in Ir/Fe/Co/Pt multilayers and their topological Hall signature”, Nature Communications 10, 696 (2019).

Publicity and Media Coverage

1. EE Times

2. A*STAR Research

3. Young Scientist Awards 2018

4. Asian Scientist Magazine

Contact

A*STAR celebrates International Women's Day

From groundbreaking discoveries to cutting-edge research, our researchers are empowering the next generation of female science, technology, engineering and mathematics (STEM) leaders.

Get inspired by our #WomeninSTEM

.png?sfvrsn=b59474e9_3)

.png?sfvrsn=c6d76497_2)

.png?sfvrsn=dd75a853_2)

.png?sfvrsn=85a7525_2)