Heterogeneous Integration

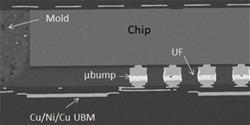

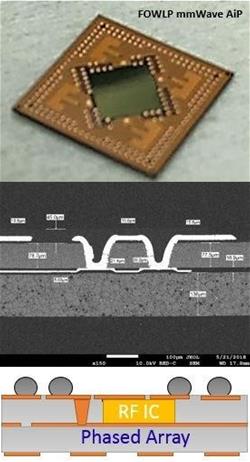

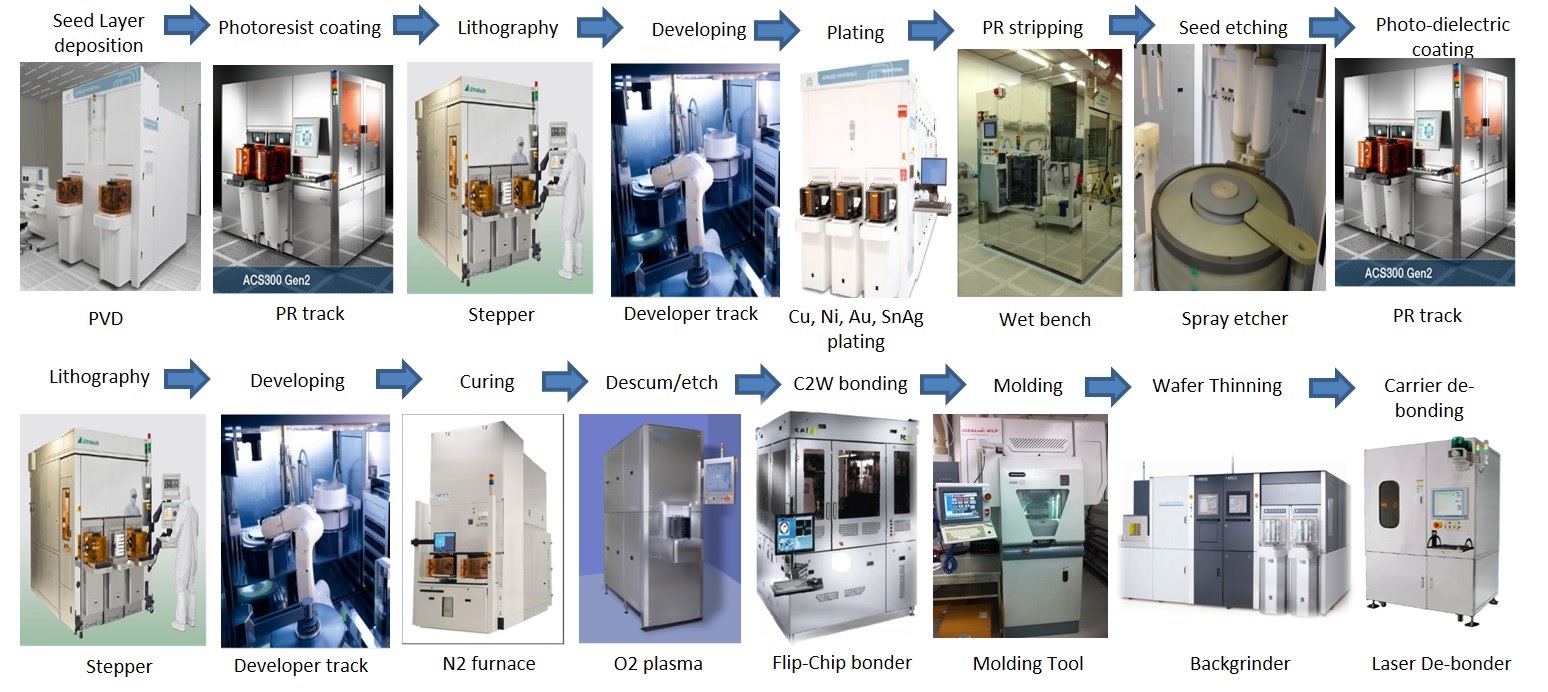

Heterogeneous Integration (HI) group uses advanced packaging platforms to integrate devices in order to solve Moore's law-predicted scaling issues. In order to maintain and further enhance progress, HI is essential for higher performance, lower latency, smaller form factors, lighter weight, less power requirement per function, and lower cost. Targeted end applications include mobile, 5G, data centres, automotive, IOT etc.

In IME, we can provide system level packaging solutions to industry partners via R&D pilot runs, service jobs, small-volume production, and technology transfer through our state-of-the-art 300mm Advanced Packaging Development line and Assembly lab.

In IME, we can provide system level packaging solutions to industry partners via R&D pilot runs, service jobs, small-volume production, and technology transfer through our state-of-the-art 300mm Advanced Packaging Development line and Assembly lab.

A*STAR celebrates International Women's Day

From groundbreaking discoveries to cutting-edge research, our researchers are empowering the next generation of female science, technology, engineering and mathematics (STEM) leaders.

Get inspired by our #WomeninSTEM