.png?sfvrsn=457f23f2_0)

Intergrated Circuit Design & Systems

Capture

Quantum sensing: We collaborate with universities and research institutes on quantum sensing research. IME’s mixed-signal design team develops high-sensitivity signal conditioning circuits with sub-nanosecond delay, as well as high-voltage actuation circuits to enable high-speed active quenching for single photon counting.

ULP sensor interface: We developed a suite of design techniques to realize ultra-low-power sensor readout with low input referred noise, wide dynamic range, and small footprint for biomedical and industrial applications. Novel direct digitization architecture which converts signals from analogue to digital domain close to the signal source is developed. This digital intensive architecture is suitable for implementation in advanced process nodes to fully leverage the advantages of technology scaling.

(a) Wearable multimodal bio-signal recording system. | (b) VCO-based Σ∆ Capacitance to Digital Converter |

Compute

Hardware accelerator: We tackle enormous data flow and computation workloads of domain-specific tasks via unorthodox approaches: (1) Tailored processing engine (PE) design (2) Novel memory & In-memory computing circuits (3) Data-driven energy-enhancement techniques.

Low-power RISC-V: We explore open-source RISC-V architecture as a platform to enable innovation in Edge AI. Our first RISC-V chip has been fabricated and tested in 40nm CMOS and we are expanding our custom instructions and silicon fabrics to harvest the full potential of our hardware accelerators (Fig. 1)

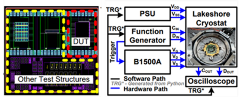

Cryogenic circuits for quantum technologies: We provide energy-efficient and high-speed IPs that enable large-scale quantum computing for the future. On top of conventional

AISC design and verification methodology, these circuits require specific modelling, compensation, and test set-up so that they are able to operate down to 4K temperature (Fig. 2).

Fig. 1 RISC-V processor with 512kB on-chip memory & coarse-grain reconfigurable PE array | Fig. 2 Cryogenic CMOS test chip and cryogenic measurement set-up |

Connect

mmWave Beamforming IC (BFIC): We are developing mmWave analog BFICs in technologies like SiGe and FDSOI for various mmWave bands (Ku, K, Ka, Q-V) for SatCOM and 5G NTN applications. We have achieved one of the best-in-class performances for noise figure (2.2-2.5dB), in the K band design.

Ka/K band BFIC with AiP: Tx: 27 - 31GHz, OP1dB 11.4dBm, PAE 10.5% and Phase error < 1.5° Rx: 18 - 21.2GHz, NF 2.2-2.55dB, Phase error < 1.5° (best in class). |

A*STAR celebrates International Women's Day

From groundbreaking discoveries to cutting-edge research, our researchers are empowering the next generation of female science, technology, engineering and mathematics (STEM) leaders.

Get inspired by our #WomeninSTEM