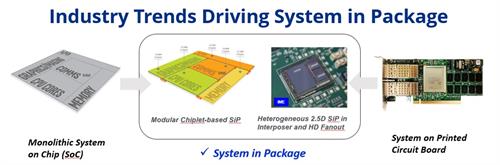

System in package

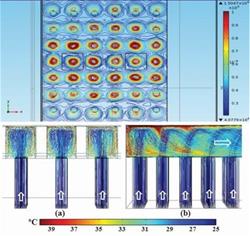

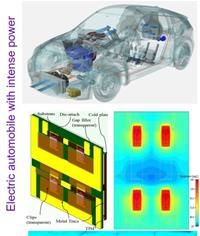

IME's System in Package (SiP) group develops novel package architectures that serve a broad range of applications such as data centres, Mobile/5G, Internet of Things, Artificial Intelligence (AI), automotive and medical technology. These package designs are virtually modelled using sophisticated multiphysics simulation tools to determine their electrical, thermal, and mechanical behaviour. The advanced-package architecture is then brought to life through the use of IME's Advanced-Package-Design-Kit (APDK) and SiP design methodology. The package is manufactured in IME's state-of-the-art 300mm Advanced Packaging Development Line and is thoroughly tested, verified, and evaluated for reliability at IME's More-than-Moore Test Center. By utilizing the SiP platform at IME, our industry partners can prototype, sample, and produce advanced packages that are tailored to their specific end applications.

A*STAR celebrates International Women's Day

From groundbreaking discoveries to cutting-edge research, our researchers are empowering the next generation of female science, technology, engineering and mathematics (STEM) leaders.

Get inspired by our #WomeninSTEM